在硬件设计中,用电子电路来实现对位的运算,以及在各种存储器中存储位。

大多数的现代电路技术都是用信号线上的高低压来表示不同的位值。

在当前的技术中,逻辑 1 使用 1.0 V 左右的高电压表示,而逻辑 0 则是用 0.0 V 左右的低电压表示。

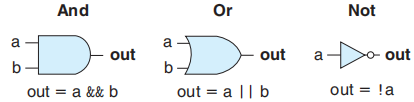

逻辑门

逻辑门是数字电路的基本计算单位,它只对单个位的数进行运算。

组合电路和 HCL 表达式

将很多逻辑门组合在一起就能构建计算块(computation block),称为组合电路。

构建组合电路有两个限制:

1, 两个或多个逻辑门的输出不能连接在一起。

2, 这个网必须是无环的。

硬件控制语言(Hardware Control Language,HCL)用来描述硬件的控制部分。

下文使用的是 HCL 的一种:Verilog。

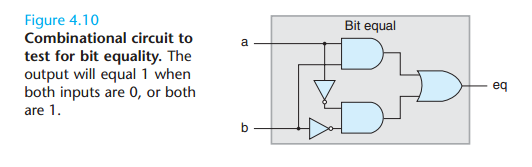

检测相等的组合电路

-

位级实现

HCL 描述:

bool eq = (a && b) || (!a && !b); -

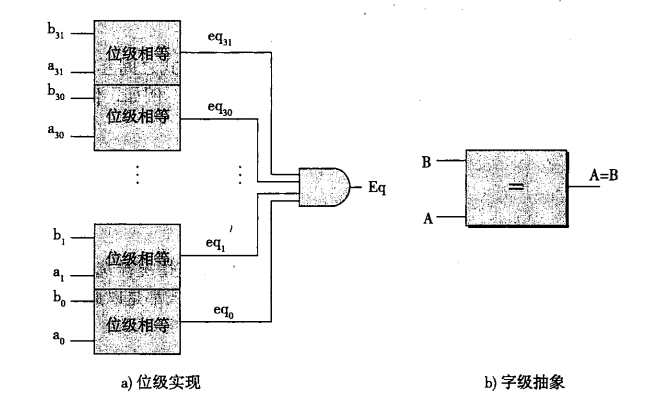

字级实现

将“字的大小”个位级实现电路的输出输入到一个 AND 门即可。

bool Eq = (A == B);

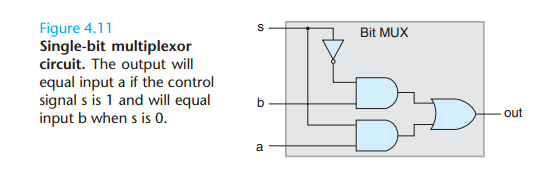

多路复用器(multiplexor, MUX)

根据控制信号,从一组信号中选出一个。

-

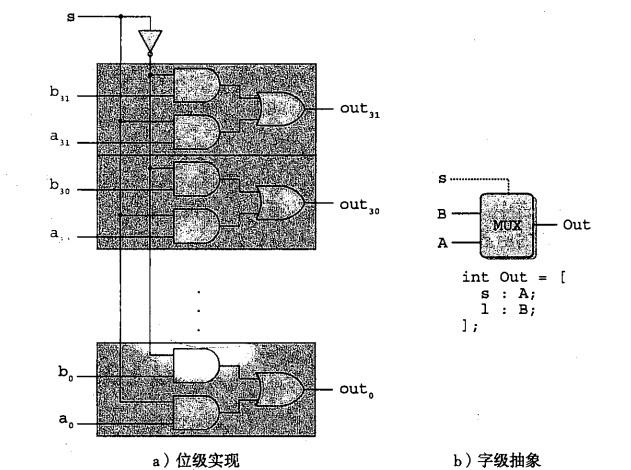

位级实现

bool out = (s && a) || (!s && b); -

字级实现

-

二选一

int Out = [ s: A; 1: B; ]; -

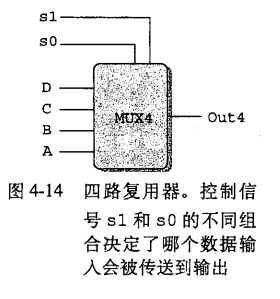

四选一

四选一需要两位控制信号(s1、s2)才能指明要选的信号。

int Out = [ !s1 && !s0: A; !s1: B; !s0: C; 1: D; ];

-

算数/逻辑单元(arithmetic logic unit,ALU)

ALU 是中央处理器(CPU)的执行单元,是所有 CPU 的核心组成部分。能实现多组算术运算和逻辑运算。

这个电路有三个输入:的两个数据输入 A 和 B,以及一个控制输入 Opcode。

根据控制输入信号,电路对数据输入执行不同的算数或逻辑运算并输出。

集合关系

在处理器设计中,很多时候需要将一个信号与多个可能的匹配值做比较,来检测该信号是哪个指令代码。

例如用一个两位的信号 code 来控制筛选 4 个信号,四选一的 MUX 在上面已经介绍过了,现在需要通过 code 产生 s1 和 s2。

假设 s1 表示 code 高位为 1,s0 表示 code 低位为 1,则有下面的 HCL 表达式:

bool s1 = code in {2, 3};

bool s0 = code in {1, 3};

小结

上文只是列举了几个组合电路的实现。

最重要的是要掌握:

- 组合电路能够根据输入信号和某种规则而进行信号输出;

- 组合电路不存储任何信息。